MODUL III: LAPORAN AKHIR 1

2. Alat dan Bahan [Kembali]

A. ALAT

B. BAHAN (PROTEUS)

a. IC 74LS112 (JK filp flop)

Gambar 3. IC 74LS112

b. Power DC

Gambar 4. Power DC

c. Switch (SW-SPDT)

Gambar 5. Switch

d. Seven Segment

Gambar 5. Seven Segment

e. IC 74LS47

3. Rangkain Simulasi [Kembali]

4. Prinsip [Kembali]

Percobaan 1 Situasi 6 menggunakan IC 74LS112 (JK Flip-flop) tetapi membutuhkan RS flip-flop agar kaki J dan K tidak terhubung. Outputnya dibaca oleh 7-segment, yang terlebih dahulu harus dihubungkan ke IC 74LS47 sebagai decoder.

Pada Percobaan 1, saklar SPDT diberi energi sehingga keluarannya adalah 1 sedangkan IC cabang RS 74LS112 aktif LOW. Jadi jam mempengaruhi output. Pada Eksperimen 1, merupakan pencacah asinkron yang memiliki input jam ayunan dari keluaran ayunan sebelumnya. Untuk penghitung ini, keluarannya tertunda atau tertunda atau berubah selama mode waktu penghitungan. Sehingga hasil flip-flop bekas apapun akan crash (perubahan kondisi dari "0" menjadi "1"). Pin MSB (output dari flip-flop terakhir dihubungkan ke dekoder cabang D) dan cabang LSB (output dari flip-flop pertama dihubungkan ke dekoder cabang A). Kemudian di segmen 7 Anda dapat melihat bahwa outputnya berurutan 0-1 yang berarti arus balik.

5. Video Rangkaian [Kembali]

6. Analisa [Kembali]

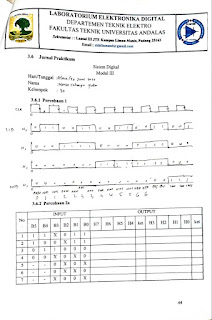

1. Analisa sinyal output yang dikeluarkan masing masing T Flip Flop?, kenapa Flip flop terakhir disebut MSD?

Jawab :

Dalam rangkaian percobaan ini, 1 adalah pencacah asinkron yang menggunakan flip-flop T, yang awalnya dipicu sebagai 1 0, kemudian sebagai H0 atau keluaran flip-flop pertama sebagai 1, karena 1 0 berarti keluarannya berubah. , jadi 1/Ho 0 akan menjadi 1 di flip-flop. Awalnya, flip-flop 2 0 1 memicu flip-flop 1, menghasilkan output 0 0.

Pada flip-flop 3, flip-flop 2 diawali dengan 0 0, sehingga hasilnya adalah 0 0.

Dan proses ini berulang sehingga hasilnya adalah :

H0 : 011001100110011001

H1 : 000111100001111000

H2 : 000000011111111000

H3 : 000000000000000111

Dan yang menyebabkan mengapa sinyal bereaksi/berubah karena ditrigger oleh 1 0 karena itu merupakan syarat aktif low.

Sinyal flip flop terakhir disebut MSB, dikarenakan sinyal tersebut mewakili nilai bit palling signifikan dalam representasi bilangan biner, MSB mewakili nilai bit terbesar dan paling signikan dalam bilangan biner.

2. Analisa kondisi falltime dan risetime pada clock terhadap output pada percobaan yang dilakukan

Jawab :

Selama percobaam ini, input logika 0 menunjukkan bahwa clock aktif, atau sering disebut aktif low.

Saat falltime, ini menunjukkan bahwa clock aktif, yang membuat output aktif, karena merupakan counter asynchronous, input dan output clock menjadi input pada flip- flop selantnya.

Saat risetime clock tidak akan aktif dikarenakan tidak memenuhi syarat dalam clock aktif yaitu active low.

.jpeg)